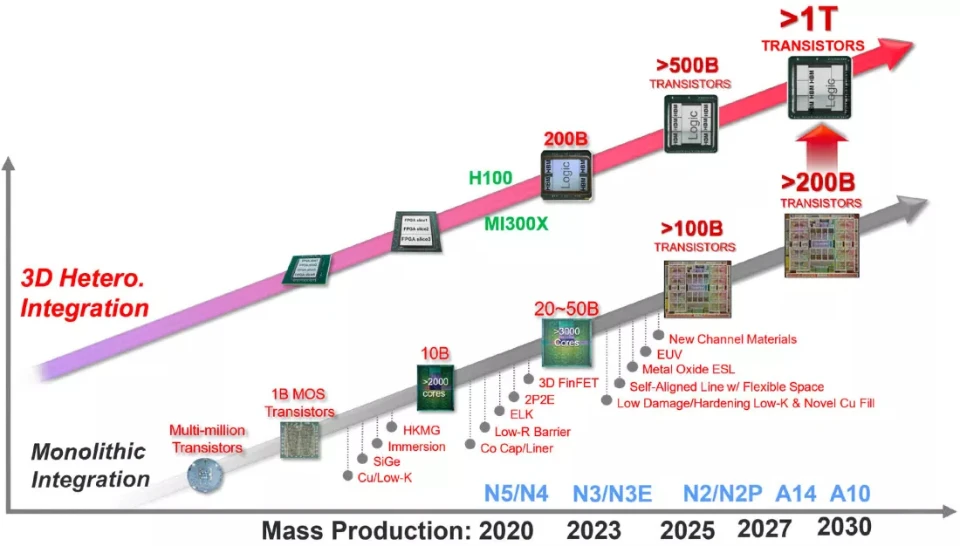

อ้างอิงจาก Techspot ในงานประชุม IEDM เมื่อเร็ว ๆ นี้ TSMC ได้ประกาศแผนงานผลิตภัณฑ์สำหรับกระบวนการผลิตเซมิคอนดักเตอร์รุ่นต่อไป ซึ่งจะนำไปสู่การออกแบบชิปเล็ตแบบเรียงซ้อน 3 มิติหลายตัวที่มีทรานซิสเตอร์ 1 ล้านล้านตัวบนแพ็คเกจชิปตัวเดียว ความก้าวหน้าทางเทคโนโลยีการบรรจุ เช่น CoWoS, InFO และ SoIC จะช่วยให้บริษัทบรรลุเป้าหมายดังกล่าว และภายในปี 2030 TSMC เชื่อว่าการออกแบบแบบโมโนลิธิกของบริษัทอาจมีทรานซิสเตอร์ถึง 2 แสนล้านตัว

TSMC เชื่อว่าจะสามารถสร้างชิป 1 นาโนเมตรได้ภายในปี 2030

GH100 ของ Nvidia ที่มีทรานซิสเตอร์ 8 หมื่นล้านตัว เป็นหนึ่งในชิปโมโนลิธิกที่มีความซับซ้อนที่สุดในตลาด อย่างไรก็ตาม เนื่องจากชิปเหล่านี้มีขนาดใหญ่ขึ้นเรื่อยๆ และมีราคาแพงขึ้น TSMC เชื่อว่าผู้ผลิตจะหันมาใช้สถาปัตยกรรมแบบหลายชิปเล็ต เช่น Instinct MI300X ของ AMD ที่เพิ่งเปิดตัว และ Ponte Vecchio ของ Intel ที่มีทรานซิสเตอร์ 1 แสนล้านตัว

ในขณะนี้ TSMC ยังคงพัฒนากระบวนการผลิต N2 และ N2P ขนาด 2 นาโนเมตร รวมถึงชิป A14 และ A10 ขนาด 1.4 นาโนเมตรต่อไป บริษัทวางแผนที่จะเริ่มการผลิตขนาด 2 นาโนเมตรภายในสิ้นปี 2025 และในปี 2028 จะเปลี่ยนไปผลิต A14 ขนาด 1.4 นาโนเมตร และมีแผนที่จะผลิตทรานซิสเตอร์ขนาด 1 นาโนเมตรภายในปี 2030

ในขณะเดียวกัน Intel กำลังพัฒนากระบวนการผลิตขนาด 2 นาโนเมตร (20A) และ 1.8 นาโนเมตร (18A) ซึ่งคาดว่าจะเปิดตัวในช่วงเวลาเดียวกัน ข้อดีอย่างหนึ่งของเทคโนโลยีใหม่นี้คือความหนาแน่นของลอจิกที่สูงขึ้น ความเร็วสัญญาณนาฬิกาที่สูงขึ้น และการรั่วไหลที่น้อยลง นำไปสู่การออกแบบที่ประหยัดพลังงานมากขึ้น

เป้าหมายของ TSMC ในการพัฒนาชิปขั้นสูงรุ่นต่อไป

ในฐานะโรงหล่อที่ใหญ่ที่สุด ในโลก TSMC มั่นใจว่ากระบวนการผลิตจะมีประสิทธิภาพเหนือกว่าทุกสิ่งที่ Intel นำเสนอ ระหว่างการประชุมผลประกอบการ ซีซี เว่ย ซีอีโอของ TSMC กล่าวว่าผลการตรวจสอบภายในยืนยันถึงการพัฒนาของเทคโนโลยี N3P และกระบวนการผลิต 3 นาโนเมตรของบริษัทพิสูจน์แล้วว่า "เทียบเท่า PPA" กับกระบวนการ 18A ของ Intel เขาคาดว่า N3P จะมีประสิทธิภาพดีกว่า แข่งขันได้ดีกว่า และมีข้อได้เปรียบด้านต้นทุนอย่างมีนัยสำคัญ

ในขณะเดียวกัน แพท เกลซิงเกอร์ ซีอีโอของ Intel อ้างว่ากระบวนการผลิต 18A ของพวกเขาจะมีประสิทธิภาพเหนือกว่าชิป 2 นาโนเมตรของ TSMC ที่เปิดตัวไปเมื่อปีก่อน แน่นอนว่าเวลาเท่านั้นที่จะพิสูจน์ได้

ลิงค์ที่มา

การแสดงความคิดเห็น (0)