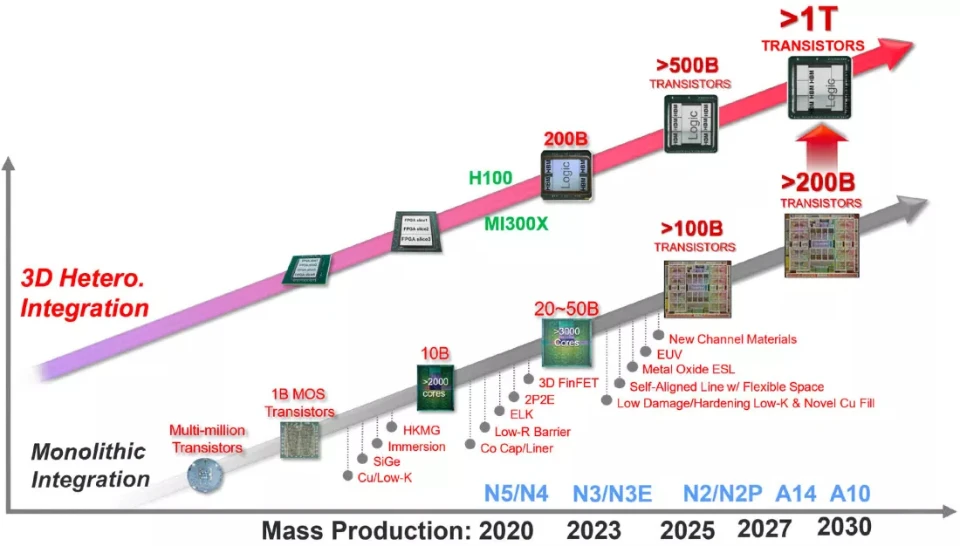

Selon Techspot , lors de la récente conférence IEDM, TSMC a annoncé une feuille de route pour ses procédés de fabrication de semi-conducteurs de nouvelle génération, qui aboutiront à la conception de multiples puces empilées en 3D, avec 1 000 milliards de transistors sur un seul boîtier. Les avancées technologiques en matière de packaging, telles que CoWoS, InFO et SoIC, permettront à l'entreprise d'atteindre cet objectif. D'ici 2030, TSMC estime que ses conceptions monolithiques pourraient atteindre 200 milliards de transistors.

TSMC estime pouvoir créer des puces de 1 nm d'ici 2030

La puce GH100 de Nvidia, dotée de 80 milliards de transistors, est l'une des puces monolithiques les plus complexes du marché. Cependant, face à la croissance continue de leur taille et de leur prix, TSMC estime que les fabricants adopteront des architectures multi-chiplets, comme l'Instinct MI300X d'AMD récemment lancé et le Ponte Vecchio d'Intel, doté de 100 milliards de transistors.

Pour l'instant, TSMC continuera de développer ses procédés de fabrication N2 et N2P en 2 nm, ainsi que ses puces A14 en 1,4 nm et A10 en 1 nm. L'entreprise prévoit de lancer la production en 2 nm d'ici fin 2025. En 2028, elle passera au procédé A14 en 1,4 nm, et d'ici 2030, elle prévoit de produire des transistors en 1 nm.

Parallèlement, Intel travaille sur des procédés 2 nm (20 A) et 1,8 nm (18 A), dont le lancement est prévu à la même période. L'un des avantages de cette nouvelle technologie est qu'elle offre une densité logique plus élevée, des fréquences d'horloge accrues et des fuites réduites, ce qui permet des conceptions plus économes en énergie.

L'objectif de TSMC est de développer la prochaine génération de puces avancées

En tant que plus grande fonderie au monde , TSMC est convaincue que ses procédés de fabrication surpasseront tout ce qu'Intel peut offrir. Lors d'une conférence téléphonique sur les résultats financiers, CC Wei, PDG de TSMC, a déclaré que des analyses internes confirmaient les améliorations apportées à la technologie N3P et que le procédé de fabrication 3 nm de l'entreprise s'avérait « comparable en PPA » au procédé 18A d'Intel. Il s'attend à ce que le N3P soit encore meilleur, plus compétitif et bénéficie d'un avantage de coût significatif.

Pendant ce temps, le PDG d'Intel, Pat Gelsinger, a affirmé que son procédé de fabrication 18A surpasserait les puces 2 nm de TSMC lancées un an plus tôt. Bien sûr, seul le temps nous le dira.

Lien source

![[Photo] Le secrétaire général To Lam assiste au 80e anniversaire de la diplomatie vietnamienne](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/8/25/3dc715efdbf74937b6fe8072bac5cb30)

Comment (0)