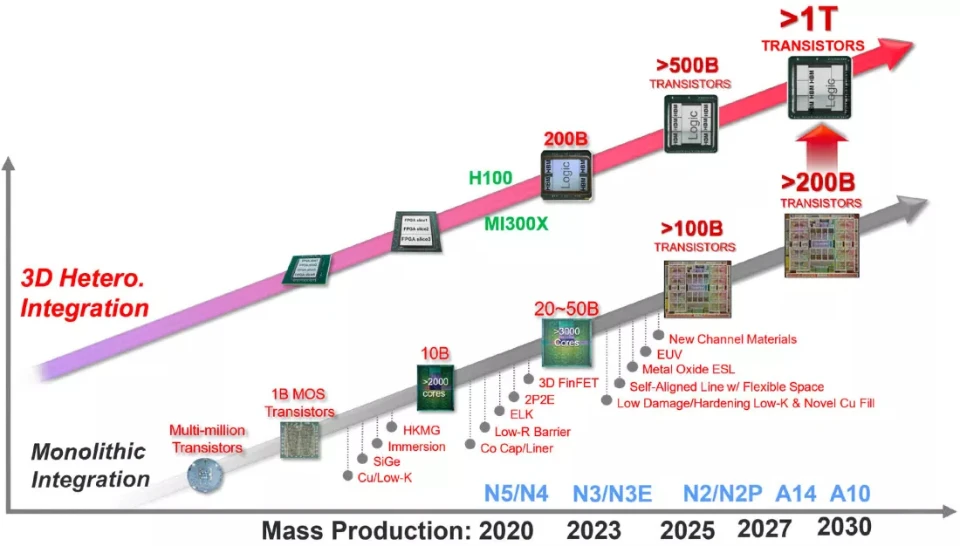

Laut Techspot hat TSMC auf der jüngsten IEDM-Konferenz eine Produkt-Roadmap für seine Halbleiterfertigungsprozesse der nächsten Generation angekündigt, die letztendlich in mehreren 3D-gestapelten Chiplet-Designs mit einer Billion Transistoren auf einem einzigen Chip-Gehäuse gipfeln soll. Fortschritte in Verpackungstechnologien wie CoWoS, InFO und SoIC werden es dem Unternehmen ermöglichen, dieses Ziel zu erreichen. Bis 2030 glaubt TSMC, dass seine monolithischen Designs 200 Milliarden Transistoren erreichen könnten.

TSMC glaubt, dass es bis 2030 1-nm-Chips herstellen kann

Nvidias GH100 mit 80 Milliarden Transistoren ist einer der komplexesten monolithischen Chips auf dem Markt. Da diese Chips jedoch immer größer und teurer werden, geht TSMC davon aus, dass Hersteller auf Multi-Chiplet-Architekturen wie den kürzlich von AMD vorgestellten Instinct MI300X und Intels 100-Milliarden-Transistor-Ponte Vecchio setzen werden.

TSMC wird zunächst seine 2-nm-Fertigungsprozesse N2 und N2P sowie die 1,4-nm-Chips A14 und A10 weiterentwickeln. Das Unternehmen plant, die 2-nm-Produktion bis Ende 2025 aufzunehmen. 2028 wird auf den 1,4-nm-A14-Prozess umgestellt, und bis 2030 plant das Unternehmen die Produktion von 1-nm-Transistoren.

Intel arbeitet derzeit an einem 2-nm-Prozess (20 A) und einem 1,8-nm-Prozess (18 A), die voraussichtlich zeitgleich auf den Markt kommen. Ein Vorteil der neuen Technologie ist die höhere Logikdichte, höhere Taktraten und geringere Leckströme, was zu energieeffizienteren Designs führt.

Das Ziel von TSMC, die nächste Generation fortschrittlicher Chips zu entwickeln

Als weltweit größte Fertigungsstätte ist TSMC überzeugt, dass seine Fertigungsprozesse alles übertreffen werden, was Intel zu bieten hat. In einer Telefonkonferenz erklärte TSMC-CEO CC Wei, interne Untersuchungen hätten die Verbesserungen der N3P-Technologie bestätigt und der 3-nm-Fertigungsprozess des Unternehmens sei „PPA-vergleichbar“ mit Intels 18A-Prozess. Er erwartet, dass N3P noch besser und wettbewerbsfähiger sein und einen deutlichen Kostenvorteil bieten wird.

Intel-CEO Pat Gelsinger behauptete unterdessen, dass der 18A-Herstellungsprozess die 2-nm-Chips von TSMC, die ein Jahr zuvor auf den Markt kamen, übertreffen werde. Das wird sich natürlich erst mit der Zeit zeigen.

[Anzeige_2]

Quellenlink

![[Foto] Die zeremonielle Artillerie ist bereit zum „Feuer“ für die zweite Paradeprobe im My Dinh National Stadium.](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/8/24/883ec3bbdf6d4fba83aee5c950955c7c)

![[Foto] Beeindruckendes Bild von 31 Flugzeugen, die während ihres ersten gemeinsamen Trainings am Himmel von Hanoi abheben](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/8/24/2f52b7105aa4469e9bdad9c60008c2a0)

Kommentar (0)